Intel помогает создавать Compute Express Link, высокоскоростной протокол для PCIe 5.0

Недавно созданный консорциум Compute Express Link (CXL) объявил о новом соединении, разработанном и предоставленном Intel, который предназначен для обеспечения согласования с кэшем интерфейса между процессорами и другими устройствами, такими как графические процессоры, FPGA и устройства памяти.

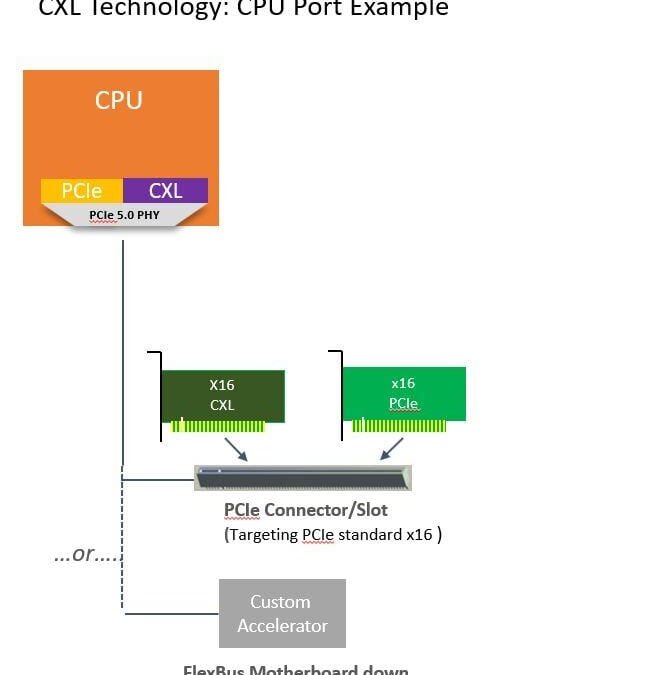

Примечательно, что новое межсоединение работает поверх интерфейса PCIe 5.0, который должен дебютировать в 2021 году, вместо интерфейса PCIe 4.0, который, как предсказывали многие, будет иметь относительно короткий срок службы.

Для реализации возможностей высокоскоростных процессоров и ускорителей требуются быстрые и гибкие межсоединения, которые могут снабжать вычислительные ядра данными для обработки. Ненасытное стремление к увеличению пропускной способности является одной из самых неприятных проблем для системных архитекторов, поскольку перемещение данных требует времени, энергии и, в конечном итоге, приводит к увеличению эксплуатационных расходов.

Соединение Compute Express Link разработано, чтобы помочь уменьшить эту нагрузку. Когерентный интерфейс кэш-памяти предназначен для центров обработки данных и позволяет использовать общие области памяти, что снижает накладные расходы и задержки. Протокол работает по шине PCIe 5.0, поэтому он электрически и механически совместим с интерфейсом, который скоро станет широко распространенным, и обеспечивает расширенные протоколы ввода-вывода и памяти, а также интерфейс когерентности.

К сожалению, более глубокие технические подробности в настоящее время недоступны, хотя консорциум заявляет, что спецификация версии 1.0 будет полностью доступна уже скоро. Первая версия полностью основана на внутренних разработках Intel за последние четыре года, но в будущем эта спецификация будет развиваться с учетом пожеланий других участников. Intel предоставила CXL данные в качестве открытого интерфейса, поэтому члены консорциума могут свободно использовать IP без лицензионных сборов.